- Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Data

- Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Tutorial

- VHDL code for half adder using Dataflow modelling: library ieee; use ieee.stdlogic1164.all; entity halfadder is port (a, b: in stdlogic; sum, carryout: out stdlogic); end halfadder; architecture dataflow of halfadder is begin sum dataflow; 2. VHDL code for half adder using Structural modelling.

- 8 to 3 encoder with priority VHDL code. This page of VHDL source code section covers 8 to 3 encoder with priority VHDL code. The block diagram and truth table of 8 to 3 encoder with priority VHDL code is also mentioned. Block Diagram of 8 to 3 encoder with priority Truth Table of 8 to 3 encoder with priority 8 to 3 encoder with priority VHDL code.

Source code for 3:8 decoder:- library IEEE; use IEEE.STDLOGIC1164.ALL; use IEEE.STDLOGICARITH.ALL; use IEEE.STDLOGICUNSIGNED.AL. Color Text Code Generator For Facebook Chat Hi friends, it is new color text code generator, which is made using JavaScript.

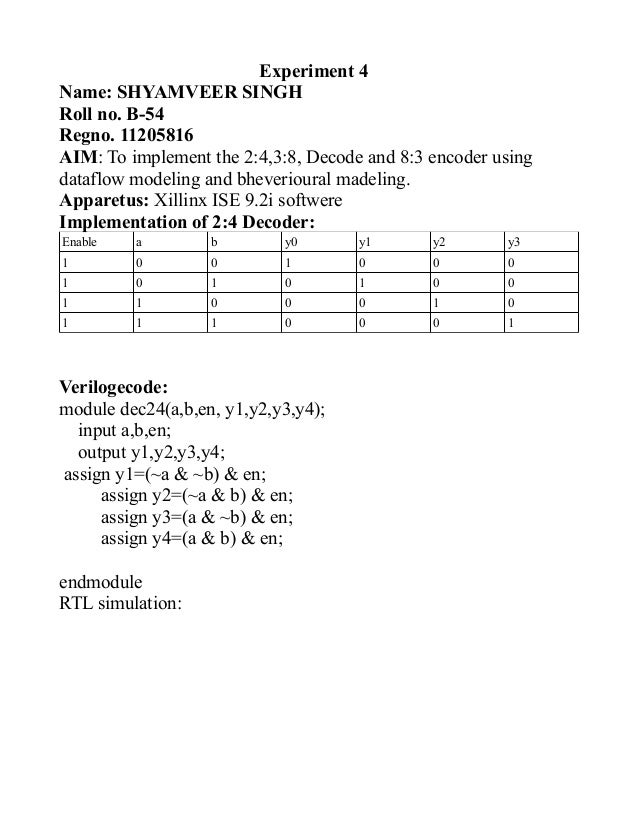

DECODER

module decodermod(e, a, b, d);

input e;

input a;

input b;

output [7:0] d;

assign d[0]=(~e)&(~a)&(~b);

assign d[1]=(~e)&(~a)&(b);

assign d[2]=(~e)&(a)&(~b);

assign d[3]=(~e)&(a)&(b);

assign d[4]=(e)&(~a)&(~b);

assign d[5]=(e)&(~a)&(b);

assign d[6]=(e)&(a)&(~b);

assign d[7]=(e)&(a)&(b);

endmodule

TEST BENCH

module decodert_b;

reg e;

reg a;

reg b;

wire [7:0] d;

decodermod uut ( .e(e),.a(a),.b(b),.d(d) );

initial begin

#10 e=1’b0;a=1’b0;b=1’b0;

#10 e=1’b0;a=1’b0;b=1’b1;

#10 e=1’b0;a=1’b1;b=1’b0;

#10 e=1’b0;a=1’b1;b=1’b1;

#10 e=1’b1;a=1’b0;b=1’b0;

#10 e=1’b1;a=1’b0;b=1’b1;

#10 e=1’b1;a=1’b1;b=1’b0;

#10 e=1’b1;a=1’b1;b=1’b1;

#10$stop;

end

endmodule

In the previous tutorial VHDL tutorial, we designed 8×3 encoder and 3×8 decoder circuits using VHDL.

(If you are not following this VHDL tutorial series one by one, you are requested to go through all previous tutorials of these series before going ahead in this tutorial)

In this tutorial,

- We shall write a VHDL program to build 1×8 demultiplexer and 8×1 multiplexer circuits

- Verify the output waveform of the program (digital circuit) with the truth table of these multiplexer and demultiplexer circuits

1×8 Demultiplexer circuit

Truth Table

(Please go through step by step procedure given in VHDL-tutorial 3 to create a project, edit and compile the program, create a waveform file, simulate the program, and generate output waveforms.)Now we shall write a VHDL program, compile it, simulate it, and get the output in a waveform. Finely, we shall verify that the output waveforms with the given truth table.

I have used the behavioral modeling style to write a VHDL program to build demultiplexer because it will be easier than the dataflow or structural modeling style.

VHDL Program

(To know more and get more details about VHDL program(s), please go through the first two tutorials, VHDL tutorial 1 and VHDL tutorial 2 of these series.)

Next, compile the above program – create a waveform file with all inputs and outputs listed – apply different input combinations – save the waveform file, and finally, simulate the project. You will get the following result.

Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Data

Simulation Waveform

As shown in the figure, one can observe that when select lines (S2, S1, S0) are “001”, the input I=0 is available in output O1=0, and when select lines are “101”, the input I=1 is available in output O5 = 1. You may verify other select line combinations with input and output.

Next, let us move on to build an 8×1 multiplexer circuit.

8×1 multiplexer circuit

Truth Table

Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Tutorial

VHDL program

Simulation waveforms

As shown in the figure, one can see that for select lines (S2, S1, S0) “011” and “100,” the inputs d3=1 and d4=1 are available in output o=1. You may verify other combinations of select lines from the truth table.

In the next tutorial, we shall design RS flip-flop and clocked RS Latch.